材料工程是启用持续逻辑缩放的关键

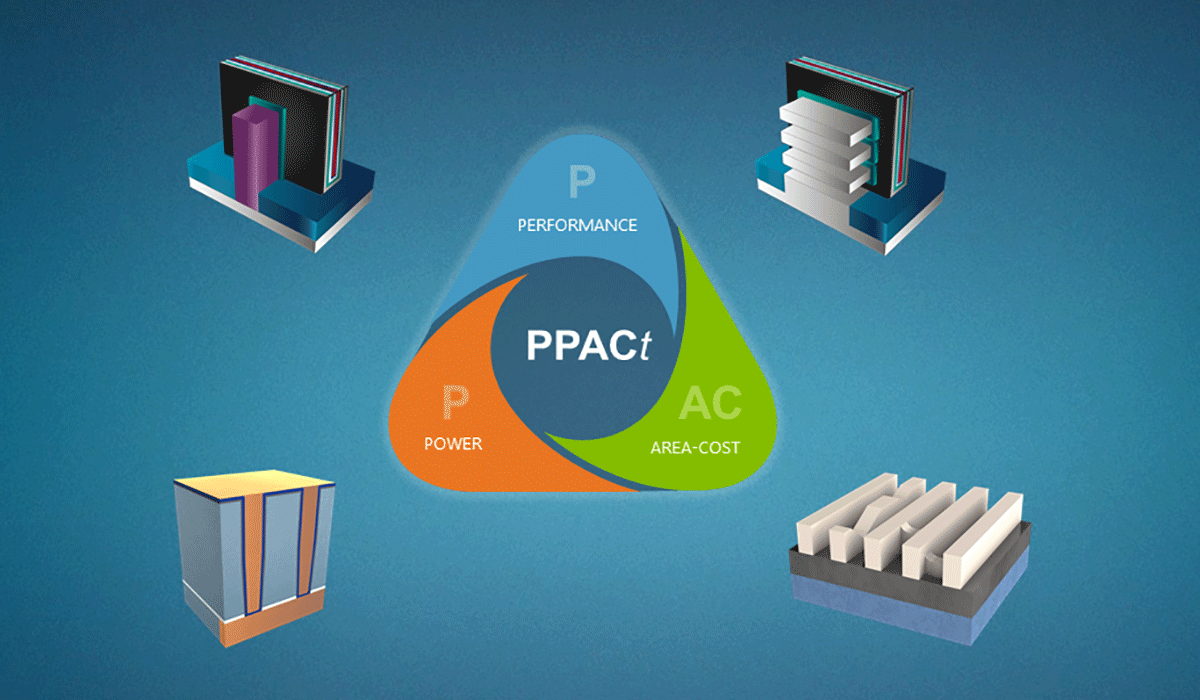

亚博最新版本应用材料托管在线逻辑主课程如今,我们展示了几种材料工程解决方案,使高级逻辑缩放能够持续改进电源,性能,面积,成本和上市时间(PPACT™)。

正如我最近博客的同事所概述的那样,多种挑战在缩放时阻碍了电力和性能改进晶体管和互连到3nm节点和超越。还有模式变异性需要新材料工程解决方案的问题。在这篇博客中,我将重点介绍Applied是如何通过基于过程步骤协同优化和集成材料解决方案(IMS™)的创新,帮助我们的客户实现高级逻辑的PPACt路线图的。我们还在帮助行业实现一种称为设计技术协同优化(DTCO)的扩展技术,这种技术将在新兴节点中越来越普遍,因为它可以在间距扩展变慢的情况下继续实现逻辑密度扩展。

晶体管缩放:将finfet扩展到5nm以上启用gate - all拐点

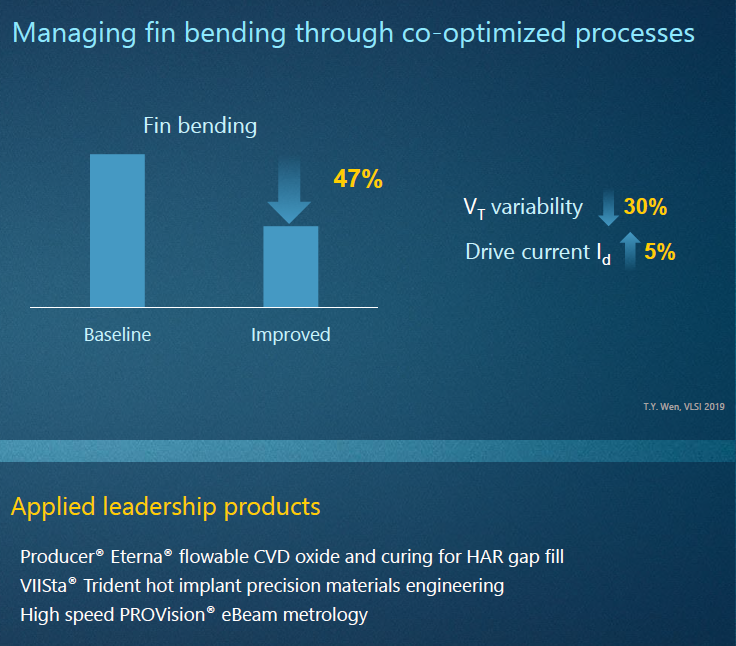

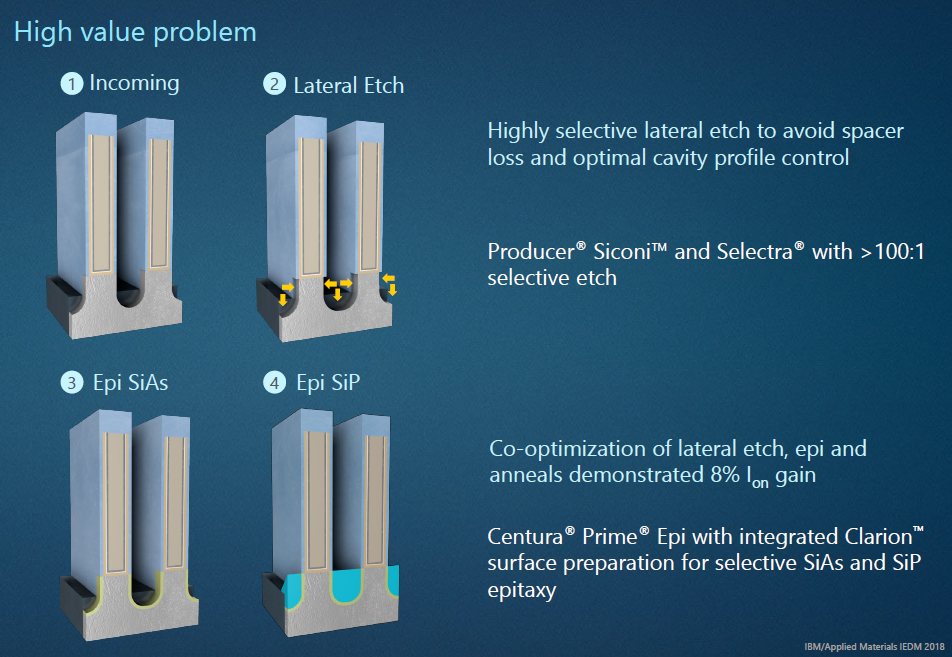

Finfet路线图具有三种重要的技术挑战:Fin弯曲,高k金属栅极(HKMG)和界面关键尺寸缩放,以及源/漏电电阻。应用是帮助解决每种新材料和过程协同优化的组合。

在制造过程中翅片弯曲导致可变性降低性能并降低功率效率。为了减轻它,我们开发了共同优化的材料工程解决方案,包括用于翅片隔离的可流动氧化物,以及共同优化的离子注入和退火步骤,所有这些都是使用应用的Provision®EBEM计量和检查技术监控的。使用这些技术,我们可以实现具有改善的均匀性的高,直的高纵横比翅片,从而将阈值电压变性降低30%并增加5%的驱动电流(参见图1)。

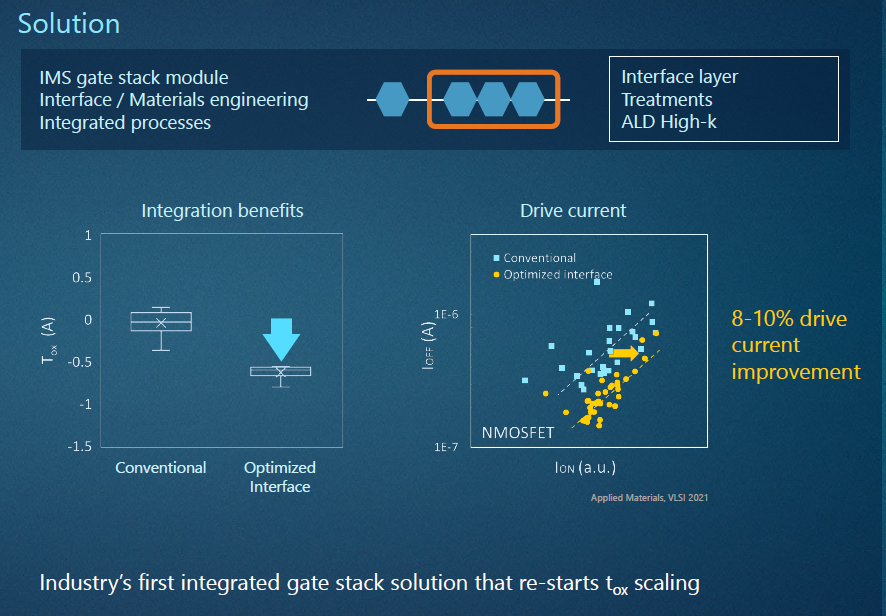

两个HKMG逻辑元素 - 接口和高k层 - 是升高晶体管驱动电流的键。但是,由于14nm节点以来,两层都没有缩放,从而创建性能瓶颈。为了解决此问题,应用开发了一种新的集成材料解决方案(IMS™),将严重的临界工艺步骤结合在真空中,以允许新的界面工程和调整程度。使用IMS™,我们已经演示了一种新的集成栅极堆叠,使等效的氧化物厚度缩放能够恢复并提高驱动电流8至10%(参见图2)。

在晶体管的源极/漏极电阻模块中,缩放使每个节点的接触面积减少了25%,导致接触电阻不可持续的增加。为了解决这一问题,Applied开发了一种新的协同优化工艺技术,使应变工程可用面积最大化(见图3)。该解决方案包括横向蚀刻,使嵌入的源漏应力源更靠近通道。此外,我们还开发了一种新型选择性砷化硅外延层。新材料和材料工程技术降低了电阻,增加了8%的驱动电流。

材料工程创新将变得更加重要,因为工业从FinFET到全面(GAA)晶体管架构,以进一步改进性能和功率(参见图4)。在GaA中,晶体管通道取向从垂直到水平移动,围绕所有四个侧面而不是三个围绕通道的栅极。控制沟道厚度对性能和功率至关重要:在从FinFET到Gaa的移动中,通道厚度控制从光刻转移到高,薄鳍片的蚀刻,以在Gaa中的外延和选择性去除,因为它们提供高度控制的生长和降低的可变性。GAA晶体管还需要通道之间的内部间隔物,并且适当的工程有助于降低电容。使用高度控制,选择性蚀刻和间隙填充工艺产生垫片。使用EBEM的计量可以帮助确保新的结构正常,最佳地形成,以实现10%至15%的预期性能增益,功率提高25%至30%。

EPI,选择性删除和EBEM Metrology是应用材料的领导领域,我们已经开发了共同优化的流程,以帮助加速GAA解决方案。亚博最新版本因此,与FinFET相比,我们预计每100K WSPM(每月晶圆开始每月)的增量收入为10亿美元。*

互连缩放:新的集成材料溶液通过电阻降低50%

互连消耗近三分之一的设备电源,占超过70%的电阻电容(RC)延迟。与每个过程节点收缩性能改善的晶体管不同,互连电线随着它们收缩而遇到更高的电阻,这反过来减少了性能并提高了功耗。在没有突破的情况下,通过电阻互连将从7nm到3nm节点增加10倍,否定晶体管缩放的益处。

解决这一挑战,今天介绍了应用材料工程中的突破称为Endura®Copper屏障SEED IMS™。这种显着的综合材料解决方案在高真空下的一个系统中结合了七种不同的工艺技术:ALD,PVD,CVD,铜回流,表面处理,接口工程和计量(见图5)。通过用选择性ALD替换共形ALD,通过替换共形ALD,解决方案在通孔界面中消除了高电阻率屏障。它还包括铜回流技术,使无效间隙填充窄特征。该解决方案可通过高达50%的通孔接触界面降低电阻,提高芯片性能和功耗。

解决材料工程和DTCO的创新模式变异性

由于EUV光刻技术与多模式技术结合使用,以创建更细的线条,在更小的节点上,模式变化的问题变得越来越严重。我们最终得到的不是我们想要的笔直、光滑的边缘,而是越来越粗糙和不均匀。在过去,这不是一个大问题,因为特征更大,边缘粗糙度的比例更小。但随着我们继续使用极紫外技术,特征和边缘粗糙度变得相当,导致随机缺陷,如开路和短路。

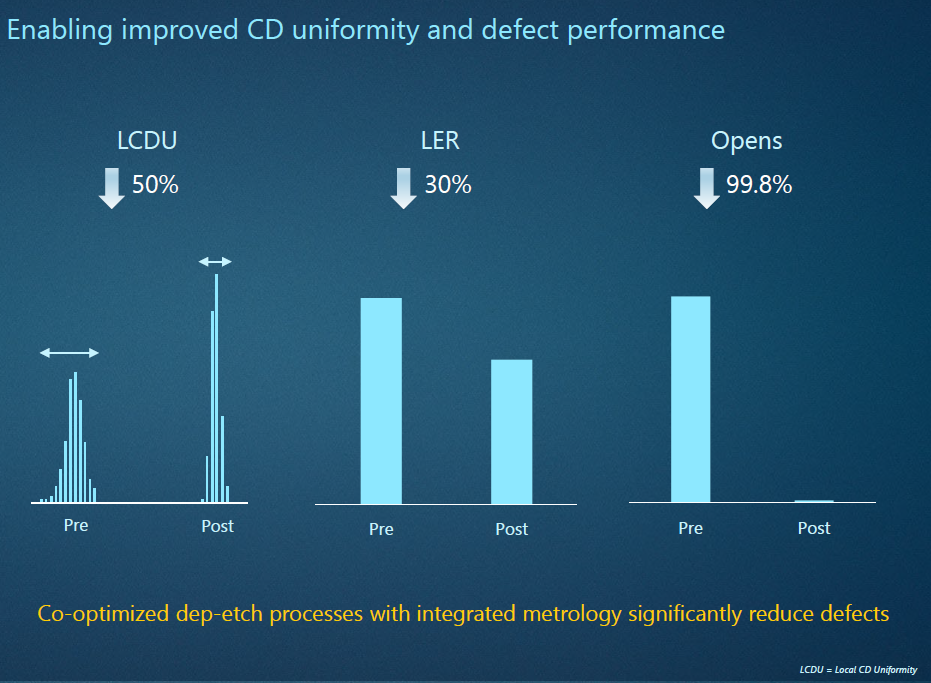

在多图案中,该行业通常使用旋转电介质和炉步骤来将光刻图案转移到器件层中。为了减少随机误差,我们正在用高质量的CVD材料更换旋转电介质,该材料在我们的Provision®EBEM计量监测过程中与我们的Sym3®蚀刻系统共同优化。事实上,我们将CVD整合到我们的蚀刻室中。一旦带有粗糙的特征进入腔室,我们选择性地沉积一层薄薄的CVD材料层,调整过程以在宽开口上储存更多材料,从而校正相邻线之间的距离。

沉积后,我们使用专门调整的蚀刻模式,蚀刻小功能比大功能快,再次减少差异。因此,通过使用我们先进的蚀刻技术协同优化CVD,我们可以平滑线并消除许多随机缺陷。我们还使用EBEMEM计量来快速测量这些微小功能的大小变化。已经证明了这种共同优化的解决方案,以实现特征尺寸的局部变化的50%,线边缘粗糙度减小30%,开路缺陷降低近100% - 其中具有健康设备产量的持续逻辑缩放(见图6)。

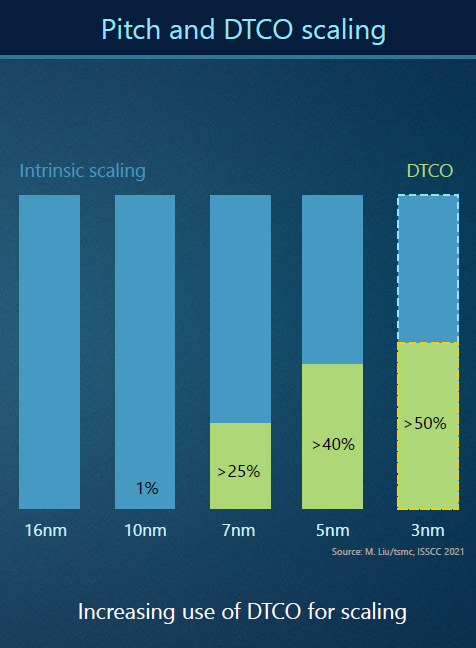

逻辑路线图依赖于逻辑密度的持续改进来降低面积成本。但是2D收缩正在放缓,并且变得更加困难。可继续将栅极和电线拉得更近的实体空间越来越少,它们越靠近,电气方面的挑战就越严重。传统摩尔定律二维缩放,也就是。音高缩放或内在缩放——在过去的几十年里为行业提供了非常好的服务。然而,展望未来,DTCO将越来越多地补充音调缩放,DTCO代表设计技术协同优化(见图7)。DTCO允许逻辑设计师使用聪明的2D和3D设计技术,在相同音调下增加逻辑密度。基于DTCO的一个关键的即将到来的变化是带有背面电力输送网络的埋地电力轨道。这种新的结构将粗大的电力线从硅片的背面或晶体管的下方输送到晶体管单元,允许进一步的二维缩放,同时降低电压损失。Applied凭借我们在金属、隔离介质、蚀刻和CMP工艺方面的专业知识,帮助实现这一技术和其他DTCO技术。

结束思想

亚博最新版本应用材料旨在为客户提供PPACT Enablement Company™,而今的主课程说明了材料工程是如何实现逻辑缩放的未来。几十年来,逻辑路线图是由传统的摩尔法2D缩放驱动的;然而,由于这种方法的益处减慢,行业正在通过基于材料工程的技术的组合来补充它,以使得能够将缩放到3nm节点并远远超出。客户正在采用“新的PLACT”,这是为应用材料创造了大量增长机会。亚博最新版本由于5nm至3nm的逻辑过渡,所应用的期望它在市场上增长25-30%。*

另一个新的PlayBook杆用于逻辑中持续的PPACT缩放是异构的设计和先进的包装,但我们将为我们的下一个主类进行讨论,该谈话是为2021年9月8日的目标。

要了解更多关于在本博客中强调的创新,请访问我们网站的此页面您可以在其中访问演示文稿和准备的备注以及活动的视频重放。

*这些是前瞻性陈述,受风险和不确定性影响。可能导致实际结果与此类声明所表达或暗示的结果存在重大差异的因素包括但不限于我们在美国证券交易委员会(SEC)文件中描述的风险和不确定性,包括我们最近的表格10-Q和8-K。所有前瞻性陈述都基于管理层当前的估计、预测和假设,我们不承担更新它们的义务。

רוציםלהצטרףלדיון吗?

הוסףתגובה:*

*התגובותהתגובותייתלעמוד.בהנחיותהדיוןובכלליהתקשורתשלנו。