解决模式可变性是进一步扩展高级逻辑芯片的关键

当我们为即将到来的应用材料做准备时亚博最新版本逻辑大师班,我的同事Mike Chudzik和Mehul Naik写了两篇博客,探讨扩展逻辑的挑战晶体管和互连.在这里,我将通过分析逻辑单元布局优化和模式可变性的问题来完成对Master类的讨论,这些问题必须得到解决,以支持逻辑领域的持续改进——成本伸缩、功率和性能。

利用设计技术协同优化缩小设备占地面积

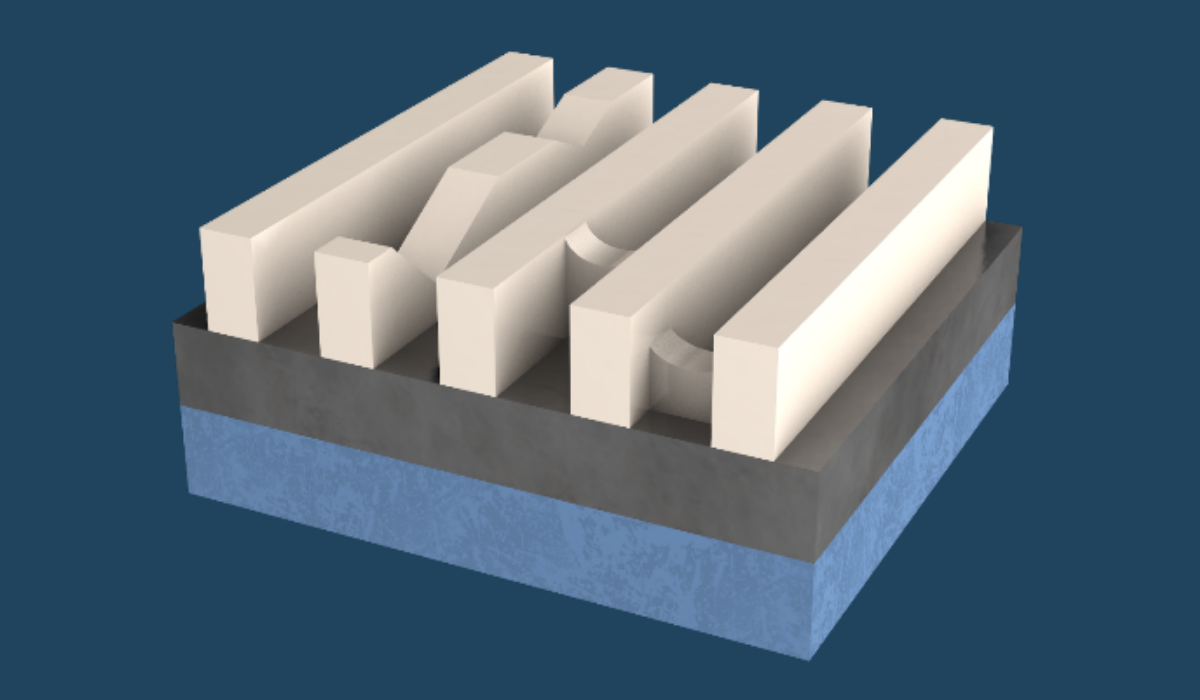

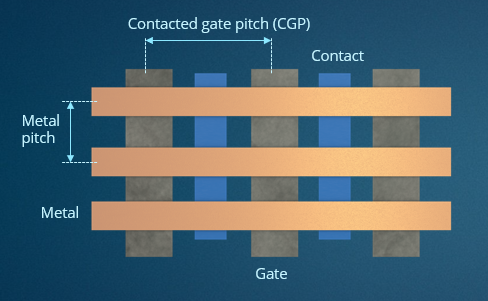

逻辑器件由大量执行基本逻辑功能的独立逻辑单元组成。每个单元都有几个晶体管栅极,它们通过金属线相互连接。在垂直方向上,栅极之间的距离我们称之为“接触栅极间距”。在水平方向上,金属线将栅极彼此连接,距离我们称之为“金属间距”。通过将这两个间距相乘,我们可以很好地测量单个单元所占的面积(见图1).

从历史上看,该行业已经使用平版印刷图案来缩放这些电池,以使栅极和导线更薄,并使它们更紧密地结合在一起。我们称之为音高缩放或内在缩放,它带来了难以置信的收益。然而,随着我们继续移动到更小的流程节点,继续拉近闸门和电线的物理不动产正在迅速消失。同时,将电气设备和结构放在如此近的位置会导致信号干扰,从而降低设备性能和功率特性。

应用程序将帮助启用一种额外的伸缩方法,该方法正在获得更多的关注,因为它在未来节点的总体伸缩好处中所占的比例越来越大。这被称为设计技术协同优化(DTCO),它允许逻辑设计师使用聪明的想法与新材料和材料工程技术,在不改变光刻和间距的情况下降低面积成本。

当我向行业外的朋友解释DTCO时,我把它比作改造房子。如果地块面积有限,我们可以增加第二层或地下室,而不是缩小卧室来腾出办公室或游戏室的空间。这可能需要额外的材料和工程——比如承重支撑以确保结构完整性——或者一些挖掘设备。在逻辑单元中,DTCO通过将关键元件(如晶体管触点)从器件的一侧移动到有源区域的顶部,使我们能够在更小的空间中放置更多功能。这叫做"主动门上的接触"该逻辑路线图最近的其他例子是“单扩散中断”,即相邻晶体管之间的双绝缘结构被一个单一的、更高质量的结构取代,以节省空间。这些方法都需要创造力和一些风险,通过使用更高质量的材料和更精确的材料工程技术来缓解。

客户期望DTCO在新兴节点中推动逻辑扩展,我将在Master类中讨论这些应用程序。

克服模式变化

如果我们能够找到方法克服一个随着我们进一步扩展而大大增加的问题:模式可变性,那么音高缩放也可以继续。感兴趣的一个特殊挑战是将EUV光刻与多图案技术相结合以创建更细的线条。

为了实现可靠性和产量以及功率、性能、面积和成本(PPAC),我们需要保持直线和平滑的边缘。在现实中,每个特征的边缘都有粗糙度和非均匀性。在过去,这并不是一个大问题,因为边缘只占特征宽度的很小百分比:我们基本上可以忽略它们。然而,随着我们继续使用EUV缩放,边缘可以占线宽的30%(见图2)。现在边缘粗糙度是关键。在光刻分辨率和线边缘粗糙度之间存在着日益增长的权衡。当我们增加多模式步骤的数量时,这种权衡变得尤为重要,因为这可能会增加非均匀边的负面影响。

路线图的挑战是创建电气问题的模式缺陷。在某些地方,金属线两侧的边缘变异性创造了如此细的特征,我们有一个“掐掉”,这创造了一个开路。在其他地方,边缘粗糙度导致相邻的线变得太近,导致它们合并并造成短路。模型工程师给这些问题起了个名字:“随机”缺陷。他们在技术会议上耗费了大量的注意力。

幸运的是,有高度创新的新型集成材料解决方案在纳米尺度上工作,帮助解决这些随机问题,并使EUV双模式成功。我会在大师课上详细介绍它们。

总之,高级逻辑可以继续使用音高缩放和DTCO进行缩放。Applied Materials已经在与我们的客户密切合作,以加速接下来的几个逻辑节点,并为芯片设计人员提供电源亚博最新版本、性能、面积成本和上市时间方面的同步改进。

想参加讨论吗?

添加新注释:*

*评论必须符合我们的要求讨论指南和交战规则.